Essay

Figure 8.4.1

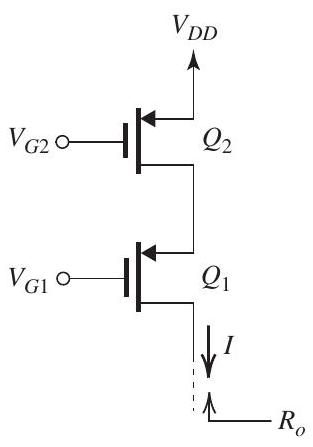

The cascode current source in Fig. 8.4.1 utilizes two identical PMOS transistors fabricated in a 0.18 - CMOS process for which , , and .

Design the circuit to obtain and and to allow for the maximum possible voltage swing at the output terminal of the current source. Utilize . Specify the values of and for and . As well, specify the required values of the dc bias voltages and . What is the maximum allowable voltage at the output?

Correct Answer:

Verified

Correct Answer:

Verified

Related Questions