Exam 2: Instructions

Prior to the early 1980s, machines were built with more and more complex instruction set. The MIPS is a RISC machine. Why has there been a move to RISC machines away from complex instruction machines?

There are number of reasons for the move towards RISC machines away from CISC. Some of them are:

Since early computers had limited memory capacities and were expensive, having a CISC instruction set enabled performing complex operations with very few instructions (encoded within a smaller memory size compared to a corresponding RISC program). Since then memories have got cheaper and there has been a lot of advances in the design of cache hierarchies (for example, a dedicated on-chip instruction cache, prefetching techniques, etc.) that permit RISC machines work-around longer instruction sequences

Writing a compiler to generate efficient code is easier for a RISC architecture than for a CISC architecture as the compiler can take advantage of a lot of registers provided by the RISC architecture than a CISC

RISC instructions are easier to pipeline than CISC instructions

Write the following sequence of code into MIPS assembler:

x = x + y + z - q;

Assume that x, y, z, q are stored in registers $s1-$s4.

The MIPS assembly sequence is as follows:

add $t0, $s1, $s2 add $t1, $t0, $s2 sub $s1, $t1, $s4

The MIPS instruction set includes several shift instructions. They include logical-shift- left, logical-shift-right, and arithmetic-shift-right. Other architectures only provide an arithmetic- shift-right instruction.

a) Why doesn't MIPS offer an "arithmetic-shift-left" opcode?

b)How would you implement in the assembler a logical-shift-left (LSL) pseudo-operation for a machine that didn't have this particular instruction? Be sure your LSL instruction can shift up to W- bits where W is the machine word size in bits.

a. The logical and arithmetic left shift operations are the same. That is why there is no need for a separate arithmetic left shift operation.

b.

Logical left shift operation corresponds to multiplication by 2. Implementing

sll $s1, $s2, n

can be done via the following loop:

li $t0, 0 li $t1, n

add $s1, $s2, 0

loop:

mul $s1, $s1, 2 sub $t0, 1

bne $t0, $t1, loop

Here the mul instruction can easily be implemented using add operations (using a loop similar to above) if it is not provided natively in the instruction set.

Convert the C function below to MIPS assembly language. Make sure that your assembly language code could be called from a standard C program (that is to say, make sure you follow the MIPS calling conventions).

unsigned int sum(unsigned int n)

{

if (n == 0) return 0; else return n + sum(n-1);

}

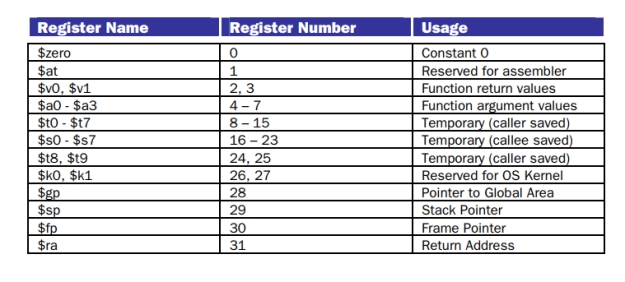

This machine has no delay slots. The stack grows downward (toward lower memory addresses). The following registers are used in the calling convention:

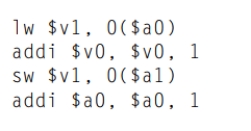

In the snippet of MIPS assembler code below, how many times is instruction memory accessed? How many times is data memory accessed? (Count only accesses to memory, not registers.)

Suppose that a new MIPS instruction, called bcp, was designed to copy a block of words from one address to another. Assume that this instruction requires that the starting address of the source block be in register $t1 and that the destination address be in $t2. The instruction also requires that the number of words to copy be in $t3 (which is > 0). Furthermore, assume that the values of these registers as well as register $t4 can be destroyed in executing this instruction (so that the registers can be used as temporaries to execute the instruction).

Do the following: Write the MIPS assembly code to implement a block copy without this instruction. Write the MIPS assembly code to implement a block copy with this instruction. Estimate the total cycles necessary for each realization to copy 100-words on the multicycle machine.

In MIPS assembly, write an assembly language version of the following C code segment:

for (i = 0; i < 98; i ++) {

C[i] = A[i + 1] - A[i] * B[i + 2]

}

Arrays A, B and C start at memory location A000hex, B000hex and C000hex respectively. Try to reduce the total number of instructions and the number of expensive instructions such as multiplies.

Some machines have a special flag register which contains status bits. These bits often include the carry and overflow bits. Describe the difference between the functionality of these two bits and give an example of an arithmetic operation that would lead to them being set to different values.

Use the register and memory values in the table below for the next questions. Assume a 32-bit machine. Assume each of the following questions starts from the table values; that is, DO NOT use value changes from one question as propagating into future parts of the question.

a) Give the values of R1, R2, and R3 after this instruction: add R3, R2, R1

b) What values will be in R1 and R3 after this instruction is executed: load R3, 12(R1)

c) What values will be in the registers after this instruction is executed: addi R2, R3, #16

In MIPS assembly, write an assembly language version of the following C code segment:

int A[100], B[100];

for (i=1; i < 100; i++) { A[i] = A[i-1] + B[i];

}

At the beginning of this code segment, the only values in registers are the base address of arrays A and B

in registers $a0 and $a1. Avoid the use of multiplication instructions-they are unnecessary.

Consider the following assembly code for parts 1 and 2.

r1 = 99

Loop:

r1 = r1 - 1

branch r1 > 0, Loop halt

(a) During the execution of the above code, how many dynamic instructions are executed?)

(b) Assuming a standard unicycle machine running at 100 KHz, how long will the above code take to complete?

Loop Unrolling and Fibonacci: Consider the following pseudo-C code to compute the fifth Fibonacci number (F(5)).

1 int a,b,i,t;

2 a=b=1; /* Set a and b to F(2) and F(1) respectively */ 3 for(i=0;i<2;i++)

4 {

5 t=a; /* save F(n-1) to a temporary location */ 6 a+=b; /* F(n) = F(n-1) + F(n-2) */

7 b=t; /* set b to F(n-1) */ 8 }

One observation that a compiler might make is that the loop construction is somewhat unnecessary. Since the the range of the loop indices is fixed, one can unroll the loop by simply writing three iterations of the loop one after the other without the intervening increment/comparison on i. For example, the above could be written as:

1 int a,b,t;

2 a=b=1;

3 t=a;

4 a+=b;

5 b=t;

6 t=a;

7 a+=b;

8 b=t;

(a) Convert the pseudo-C code for both of the snippets above into reasonably efficient MIPS code. Represent each variable of the pseudo-C program with a register. Try to follow the pseudo-C code as closely as possible (i.e. the first snippet should have a loop in it, while the second should not).

(b) Now suppose that instead of the fifth Fibonacci number we decided to compute the 20th. How many static instructions would there be in the first version and how many would there be in the unrolled version? What about dynamic instructions? You do not need to write out the assembly for this part.

Filters

- Essay(0)

- Multiple Choice(0)

- Short Answer(0)

- True False(0)

- Matching(0)