Essay

Caches and Address Translation. Consider a 64-byte cache with 8 byte blocks, an associativity of 2 and LRU block replacement. Virtual addresses are 16 bits. The cache is physically tagged. The processor has 16KB of physical memory.

(a) What is the total number of tag bits?

(b) Assuming there are no special provisions for avoiding synonyms, what is the minimum page size?

(c) Assume each page is 64 bytes. How large would a single-level page table be given that each page requires 4 protection bits, and entries must be an integral number of bytes.

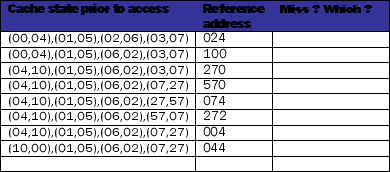

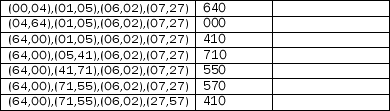

(d) For the following sequence of references, label the cache misses.Also, label each miss as being either a compulsory miss, a capacity miss, or a conflict miss. The addresses are given in octal (each digit represents 3 bits). Assume the cache initially contains block addresses: 000, 010, 020, 030, 040, 050, 060, and 070 which were accessed in that order

(e) Which of the following techniques are aimed at reducing the cost of a miss: dividing the current block into sub-blocks, a larger block size, the addition of a second level cache, the addition of a victim buffer, early restart with critical word first, a writeback buffer, skewed associativity, software prefetching, the use of a TLB, and multi-porting.

(e) Which of the following techniques are aimed at reducing the cost of a miss: dividing the current block into sub-blocks, a larger block size, the addition of a second level cache, the addition of a victim buffer, early restart with critical word first, a writeback buffer, skewed associativity, software prefetching, the use of a TLB, and multi-porting.

(f) Why are the first level caches usually split (instructions and data are in different caches) while the L2 is usually unified (instructions and data are both in the same cache)?

Correct Answer:

Verified

a. The cache is 64-bytes with 8-byte blo...View Answer

Unlock this answer now

Get Access to more Verified Answers free of charge

Correct Answer:

Verified

View Answer

Unlock this answer now

Get Access to more Verified Answers free of charge

Q2: How many total SRAM bits will be

Q3: Do the same thing as in Part

Q4: High associativity in a cache reduces compulsory

Q5: A two part question<br>(a) Why is miss

Q6: Caching. "One of the keys to happiness

Q8: For a data cache with a 92%

Q9: In what pipeline stage is the branch

Q10: Design a 8-way set associative cache that

Q11: Caches: Misses and Hits<br>int i;<br>int a[1024*1024]; int

Q12: Calculate the performance of a processor taking