Essay

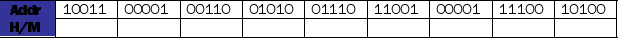

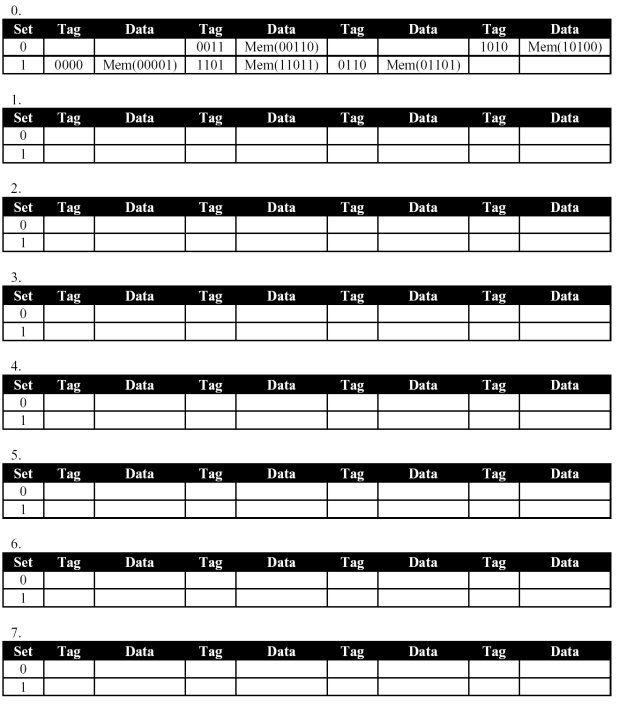

Do the same thing as in Part A, except for a 4-way set associative cache. Assume 00110 and 11011 were the last two addresses to be accessed. Use the Least Recently Used replacement policy.

Correct Answer:

Verified

Correct Answer:

Verified

Related Questions

Q1: TLB's are typically built to be fully-associative

Q2: How many total SRAM bits will be

Q4: High associativity in a cache reduces compulsory

Q5: A two part question<br>(a) Why is miss

Q6: Caching. "One of the keys to happiness

Q7: Caches and Address Translation. Consider a 64-byte

Q8: For a data cache with a 92%

Q9: In what pipeline stage is the branch

Q10: Design a 8-way set associative cache that

Q11: Caches: Misses and Hits<br>int i;<br>int a[1024*1024]; int