Essay

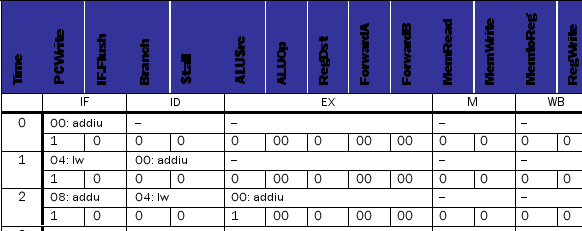

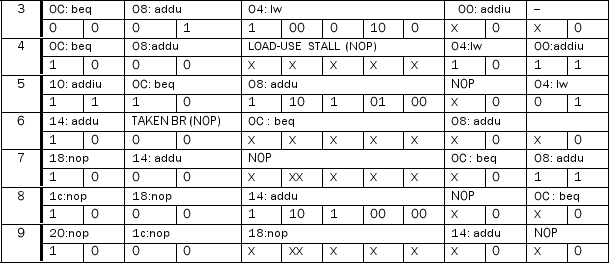

Consider the datapath below. This machine does not support code with branch delay slots. (It predicts not-taken with a 1-cycle penalty on taken branches.) For each control signal listed in the table below, determine its value at cycles 3 through 9, inclusive. Also, show the instruction occupying each stage of the pipeline in all cycles. (Assume the IF/ID write-enable line is set to the inverse of the Stall signal.)

The initial state of the machine is:

PC = 0

All pipeline registers contain 0s

All registers in the register file contain 0s. The data memory contains 0s in all locations The instruction memory contains:

00: addiu $3, $zero, 4 04: lw $4, 100($3)

08: addu $2, $4, $3

0C: beq $4, $zero, 0x14 10: addiu $3, $3, 1

14: addu $2, $2, $3

all other locations contain 0

Use data forwarding whenever possible. All mux inputs are numbered vertically from "top" to "bottom" starting at 0 as you look at the datapath in the proper landscape orientation. Also, the values for ALUOp are:

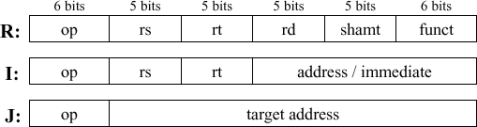

Instruction formats:

Instruction formats:

Correct Answer:

Verified

Correct Answer:

Verified

Q11: You are given a 4-stage pipelined

Q12: This is a three-part question about critical

Q13: Forwarding logic design. For this problem you

Q14: Branch Prediction. Consider the following sequence of

Q15: Pipelining is used because it improves instruction

Q16: This is a three-part question about critical

Q18: Using any ILP optimization, double the performance

Q19: The classic 5-stage pipeline seen in Section

Q20: Consider the following assembly language code:<br>I0: ADD

Q21: This is a three-part question about