Essay

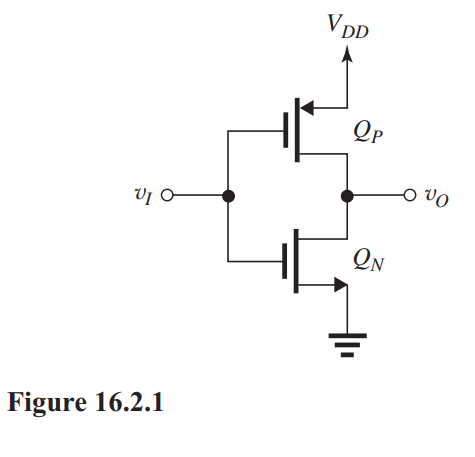

The CMOS inverter shown in Fig. 16.2.1 has and is fabricated in a process for which , and . For this problem, neglect the Early effect. Both and use the minimum channel length allowed. For .

(a) Find the dimensions that must have in order for the inverter switching to occur at .

(b) What are the noise margins of the inverter?

(c) What current flows in and at the switching point?

(d) For , what is the maximum current that can sink while is limited to ?

Correct Answer:

Verified

Correct Answer:

Verified

Q1: <img src="https://d2lvgg3v3hfg70.cloudfront.net/TBO1243/.jpg" alt="

Q2: <img src="https://d2lvgg3v3hfg70.cloudfront.net/TBO1243/.jpg" alt="

Q4: <img src="https://d2lvgg3v3hfg70.cloudfront.net/TBO1243/.jpg" alt="

Q5: <img src="https://d2lvgg3v3hfg70.cloudfront.net/TBO1243/.jpg" alt="

Q6: In the cross-coupled oscillator circuit shown

Q7: <img src="https://d2lvgg3v3hfg70.cloudfront.net/TBO1243/.jpg" alt="

Q8: <img src="https://d2lvgg3v3hfg70.cloudfront.net/TBO1243/.jpg" alt="

Q9: <img src="https://d2lvgg3v3hfg70.cloudfront.net/TBO1243/.jpg" alt="