Essay

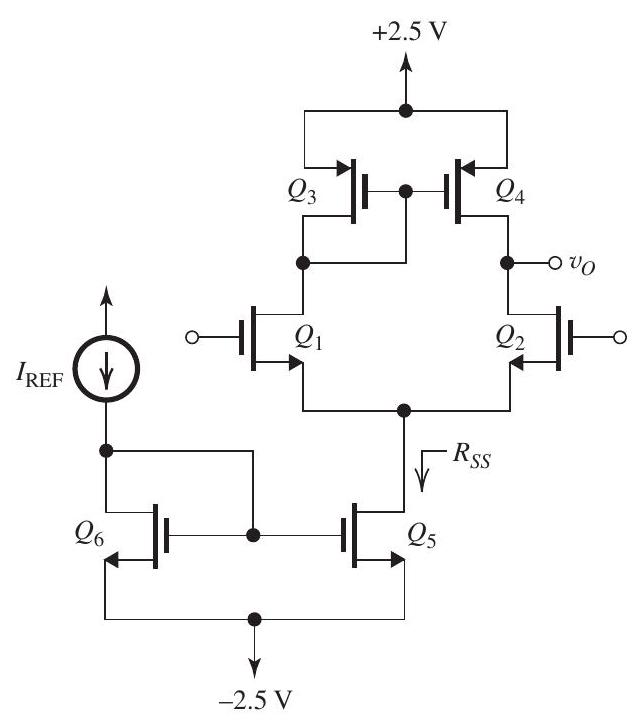

Figure 9.7.1

The current-mirror-loaded CMOS amplifier shown in Fig. 9.7.1 is fabricated in a technology for which , and . Transistors and are matched, and are matched, and and are matched. The ratios of all devices are selected so that all operate at the same .

(a) Starting from

and

show that

and

(b) To obtain a differential gain of , find the overdrive voltage at which the transistors should be operated. Also, find the resulting CMRR in .

(c) Using a reference current , find the required for each of the six transistors.

(d) With both input terminals grounded, what dc voltage occurs at the output (neglecting the Early effect)? Hence, compute the systematic input offset voltage.

(e) Find the input common-mode range.

(f) If the input differential signal is riding on an input common-mode voltage of , what is the maximum allowable output voltage swing in both directions? Hence, find the peak-to-peak amplitude of the largest sine-wave signal that can be applied between the two input terminals (without dc offset compensation).

Correct Answer:

Verified

Correct Answer:

Verified

Q1: <img src="https://d2lvgg3v3hfg70.cloudfront.net/TBO1243/.jpg" alt="

Q3: Refer to Figure 9.10.1 below. <br>

Q4: <img src="https://d2lvgg3v3hfg70.cloudfront.net/TBO1243/.jpg" alt="

Q5: <img src="https://d2lvgg3v3hfg70.cloudfront.net/TBO1243/.jpg" alt="

Q6: <img src="https://d2lvgg3v3hfg70.cloudfront.net/TBO1243/.jpg" alt="

Q7: <img src="https://d2lvgg3v3hfg70.cloudfront.net/TBO1243/.jpg" alt="

Q8: <img src="https://d2lvgg3v3hfg70.cloudfront.net/TBO1243/.jpg" alt="

Q9: <img src="https://d2lvgg3v3hfg70.cloudfront.net/TBO1243/.jpg" alt="

Q10: <img src="https://d2lvgg3v3hfg70.cloudfront.net/TBO1243/.jpg" alt="