Exam 9: Counters

Exam 1: Introductory Concepts75 Questions

Exam 2: Number Systems, Operations, and Codes49 Questions

Exam 3: Logic Gates56 Questions

Exam 4: Boolean Algebra and Logic Simplification46 Questions

Exam 5: Combinational Logic Analysis38 Questions

Exam 6: Functions of Combinational Logic46 Questions

Exam 7: Latches, Flip-Flops, and Timers38 Questions

Exam 8: Shift Registers40 Questions

Exam 9: Counters50 Questions

Exam 10: Programmable Logic30 Questions

Exam 11: Data Storage49 Questions

Exam 12: Signal Conversion and Processing46 Questions

Exam 13: Data Transmission99 Questions

Exam 14: Data Processing and Control127 Questions

Exam 15: Integrated Circuit Technologies40 Questions

Select questions type

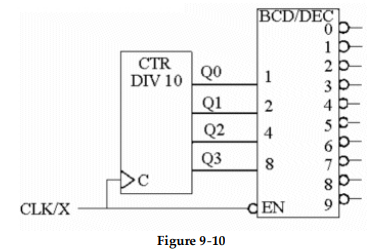

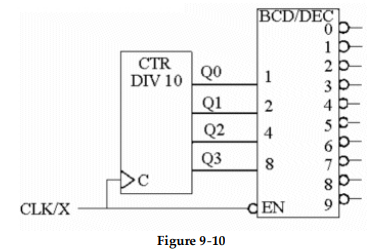

-The 'X' in the CLK/X input in Figure 9- 10 is normally called the _______ , and, in this example, is an active _______level.

-The 'X' in the CLK/X input in Figure 9- 10 is normally called the _______ , and, in this example, is an active _______level.

(Multiple Choice)

4.9/5  (38)

(38)

In order to check the CLR function of a counter, which action should be taken?

(Multiple Choice)

4.7/5  (43)

(43)

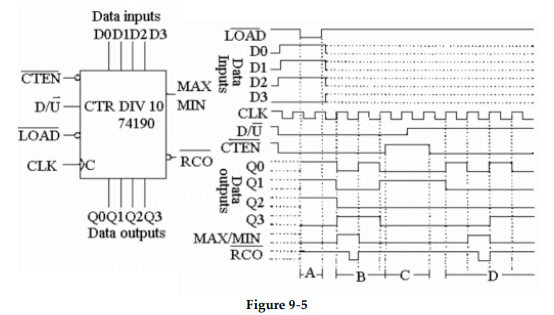

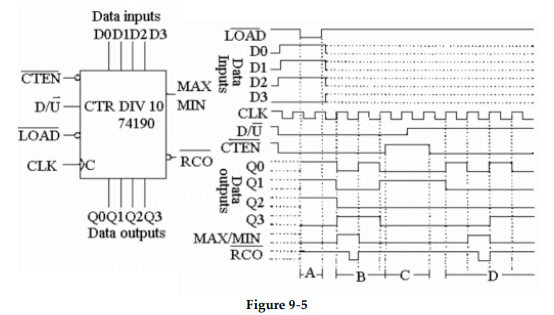

-What function does the counter shown in Figure 9- 5 perform during period A on the timing diagram?

-What function does the counter shown in Figure 9- 5 perform during period A on the timing diagram?

(Multiple Choice)

4.8/5  (38)

(38)

The register output expression Q0 = D0 indicates that the output Q0 will assume the value of the D0 input on the clock pulse.

(True/False)

5.0/5  (33)

(33)

Which of the following procedures would be used to check the parallel loading feature on a counter?

(Multiple Choice)

4.8/5  (29)

(29)

-The purpose of the connection between 'C' of the 'CTR DIV 10' circuit and the 'EN' of the 'BCD/DEC' circuit in Figure 9- 10 is to _______ and is referred to as _______ .

-The purpose of the connection between 'C' of the 'CTR DIV 10' circuit and the 'EN' of the 'BCD/DEC' circuit in Figure 9- 10 is to _______ and is referred to as _______ .

(Multiple Choice)

4.8/5  (36)

(36)

Basic counters can be cascaded to increase the number of count states the counter can produce.

(True/False)

4.8/5  (37)

(37)

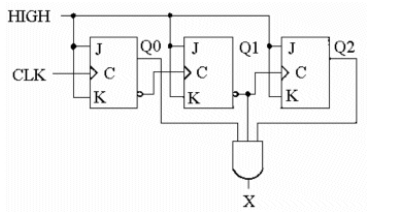

What decimal value is required to produce an output at 'X' in this circuit?

(Multiple Choice)

4.8/5  (28)

(28)

Another term used to describe up/down counters is bidirectional.

(True/False)

4.7/5  (41)

(41)

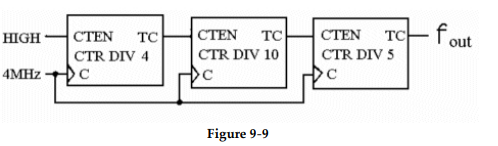

-What is the output frequency of the counter in Figure 9- 9?

-What is the output frequency of the counter in Figure 9- 9?

(Multiple Choice)

4.9/5  (40)

(40)

Once an up/down counter begins its count sequence, it cannot be reversed.

(True/False)

4.8/5  (32)

(32)

-The counter in Figure 9- 5 is counting DOWN; when the count reaches zero, the MAX/MIN output will go ________.

-The counter in Figure 9- 5 is counting DOWN; when the count reaches zero, the MAX/MIN output will go ________.

(Multiple Choice)

4.8/5  (41)

(41)

The term synchronous refers to events that do not occur at the same time.

(True/False)

4.9/5  (42)

(42)

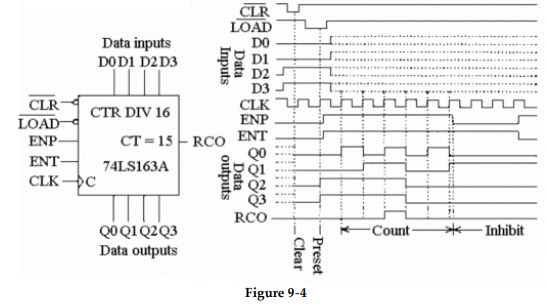

-What is the meaning of the label 'CTR DIV 16' on the 74LS163A diagram shown in Figure 9- 4?

-What is the meaning of the label 'CTR DIV 16' on the 74LS163A diagram shown in Figure 9- 4?

(Multiple Choice)

4.9/5  (42)

(42)

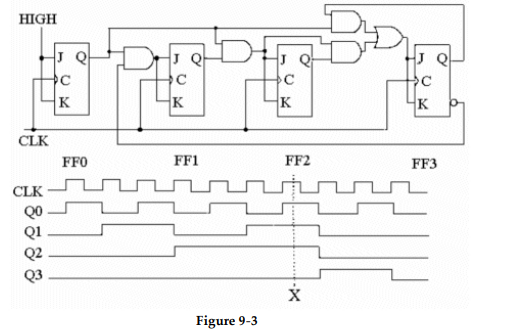

-The circuit shown in Figure 9- 3 represents a(n) __________ .

-The circuit shown in Figure 9- 3 represents a(n) __________ .

(Multiple Choice)

4.9/5  (36)

(36)

A decade counter counts from zero (0) through decimal __________.

(Multiple Choice)

5.0/5  (35)

(35)

Which of the following statements best describes the operation of an UP/DOWN SYNCHRONOUS COUNTER?

(Multiple Choice)

4.9/5  (38)

(38)

Showing 21 - 40 of 50

Filters

- Essay(0)

- Multiple Choice(0)

- Short Answer(0)

- True False(0)

- Matching(0)